使用VisualSim对雷达信号处理系统进行架构评估

1. 总体情况

VisualSim是一款主要面向电子系统和元器件结构、性能评估的建模、仿真工具。通过VisualSim,设计师可以构建目标系统的图形化虚拟模型,开展性能、功耗和功能分析。

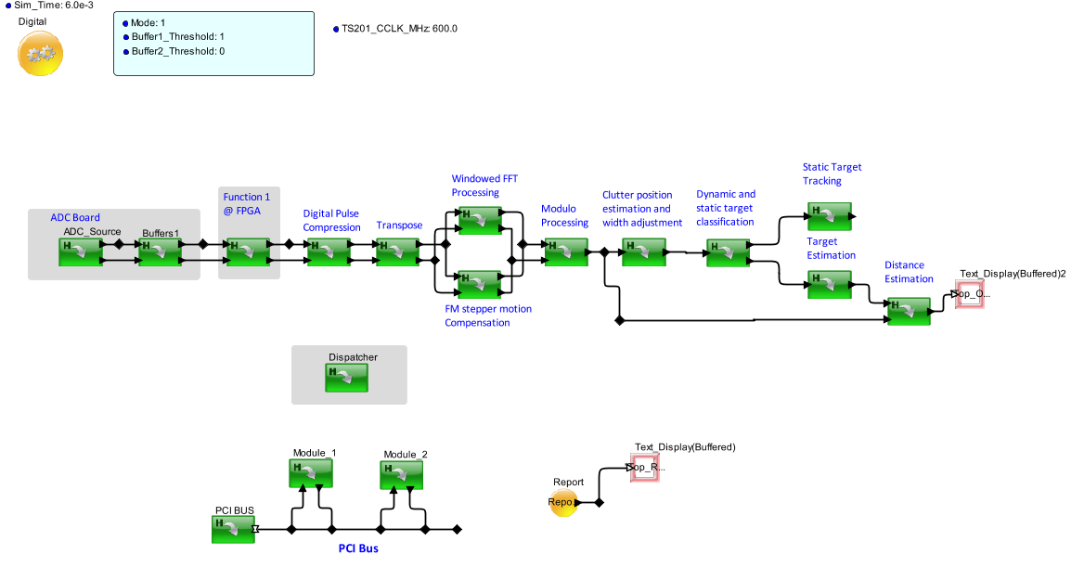

本案例是一个雷达信号处理系统模型,由硬件结构和系统行为两部分组成,用于评估雷达信号处理系统在不同工作模式下,硬件结构中数字信号处理器(Digital Signal Processor,DSP)和总线工况。模型中的所有模块均为VisualSim內建模块。

雷达信号处理系统的功能如图所示,依据脉冲重复间隔(Pulse Repetition Interval,PRI)和相干处理间隔(Coherent Processing Interval,CPI)的不同配置组合,形成三种工作模式。

雷达信号处理的硬件由DSP、PCI控制器和FPGA组成。两个DSP组成一簇,两簇组成一个模块,共两个模块通过PCI总线连接在一起。每个DSP的LINK端口连接到FPGA上,通过FPGA上的逻辑实现各个DSP LINK端口的互联。

2. 仿真模型

在VisualSim中完成的模型如图2所示。模型可分为雷达信号功能行为(图Dispatcher上部框图)、硬件架构(图Dispatcher下部框图)、映射模块(图Dispatcher)三个部分。

由于雷达信号处理系统比较复杂,因此无论是功能行为还是硬件结构均采用了层次化的设计方法,即将实现一部分功能的模块封装成一个整体。在VisualSim中使用层次化设计,将复杂的系统分割为多个小部分,既降低了建模复杂度,也有利于突出模型主体、便于维护和修改。

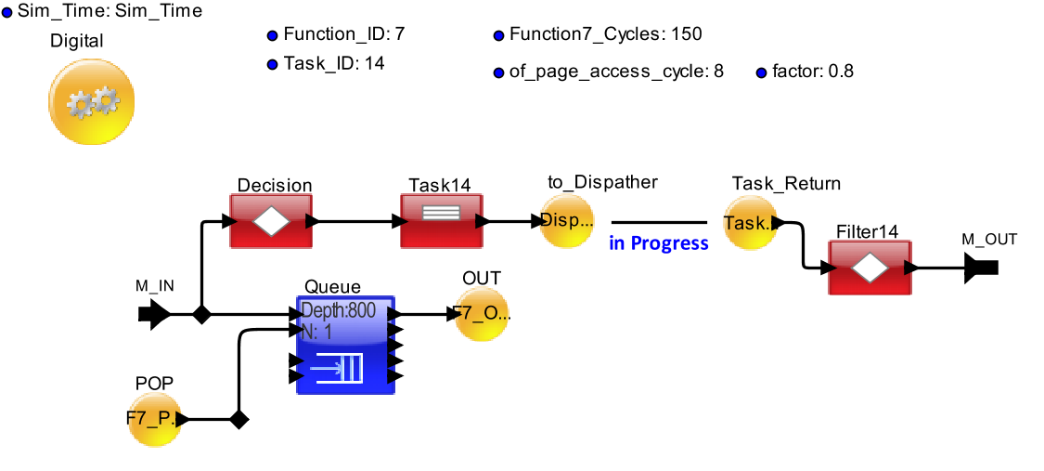

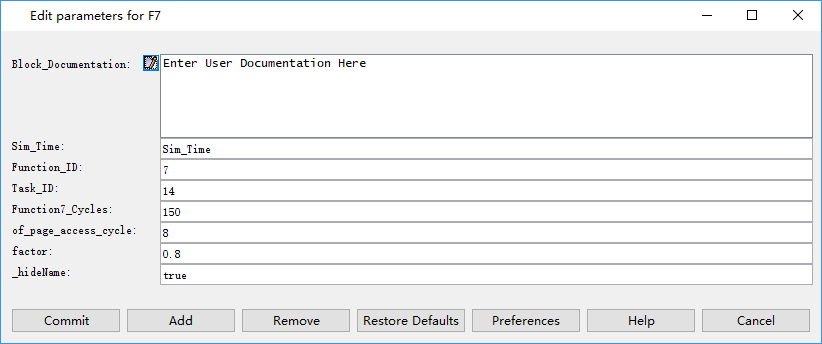

在层次化设计中,底层的设计组件为了便于配置和提高仿真速度,可是设置底层的参数和独立的仿真引擎,底层的参数可以在顶层显示和修改。例如,对于雷达信号处理功能行为里面的杂波估计模块,其内部结构如图(a)所示,可以看到,在该模块内部定义了一个数字仿真引擎,同时设置了仿真时间(Sim_Time)等多个参数。这些参数在上一层模型的参数配置界面中可以显示和修改,如图(b)所示。

(a)雷达杂波估计模块的内部

(b)雷达杂波估计模块的可配置参数

3. 仿真过程及结果

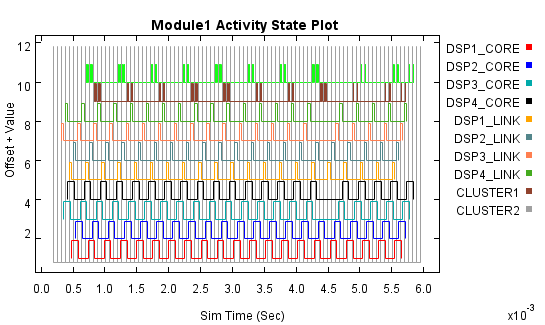

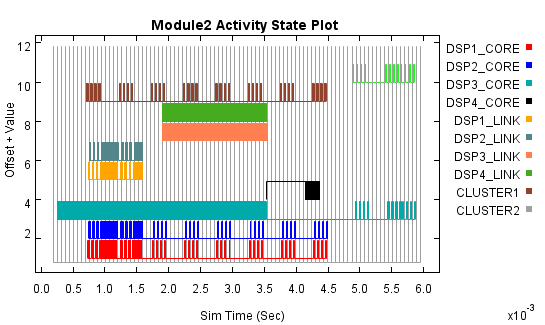

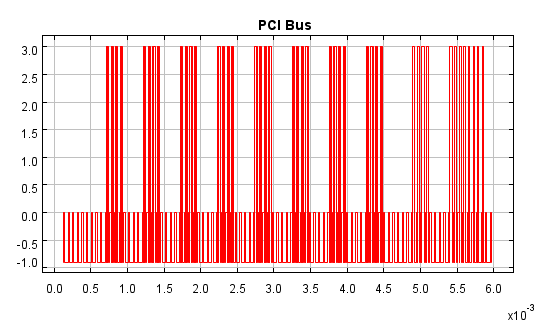

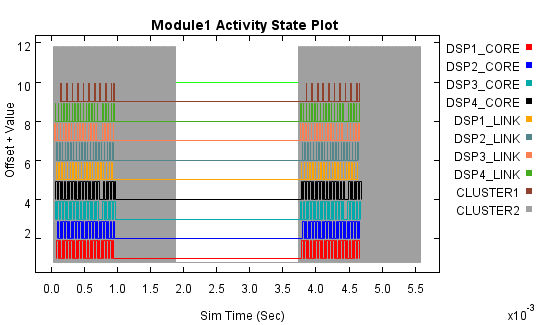

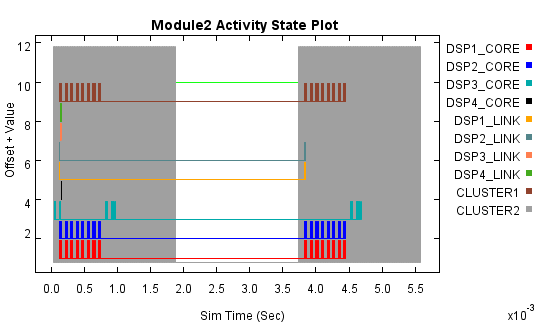

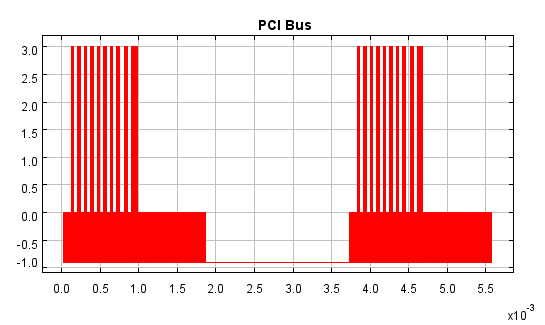

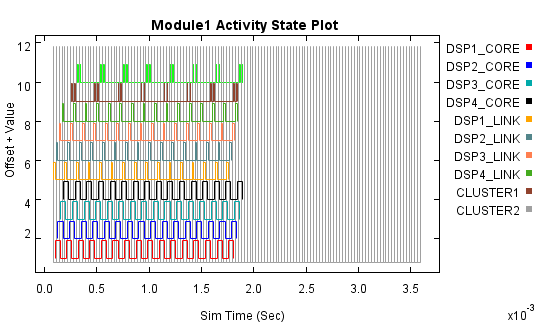

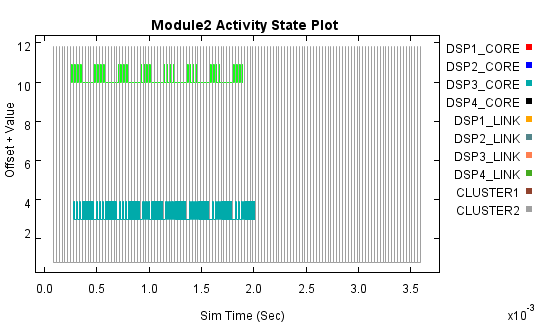

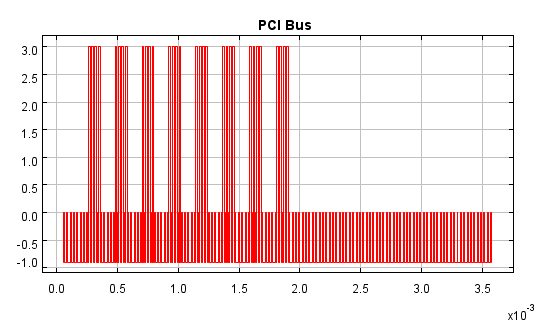

通过仿真,可以看到该雷达信号处理系统分别工作在三种不同模式时,两个DSP模块及PCI总线的工况,如图1、2、3所示。从图中可以看出,当雷达信号处理系统工作在模式1时,DSP模块1中的4个DSP工作负载基本相同,而DSP模块2中的4个DSP工作负载相差很大;工作在模式2时,DSP模块1和DSP模块2呈现出比较明显的突发特性,两次突发处理间存在比较大的间隙,可以考虑在此期间加入其它有利于雷达信号处理系统的技术,如低功耗技术;工作在模式3时,DSP模块1与工作模式1时类似,负载比较平静,而DSP模块2中仅需要core3启动处理即可,是负载最小的工况。

(a)

(b)

(c)

图1 雷达信号处理系统工作在模式1中,两个DSP模块的工况

(a)

(b)

(c)

图2 雷达信号处理系统工作在模式2中,两个DSP模块的工况

(a)

(b)

(c)

图3 雷达信号处理系统工作在模式2中,两个DSP模块的工况