1. 处理器建模与仿真的意义

在处理器设计和计算机体系结构研究中,建模与仿真是最重要的研究方法之一。使用建模与仿真方法,处理器架构师可以方便、快捷地评估不同结构或资源配置下的处理器功能和性能,从而节省处理器的研发成本并缩短上市时间。另外,使用建模与仿真的方法对处理器体系结构进行评估比制造一个处理器样品来进行评估具有更大的灵活性,因为建模和仿真可以精确地评估一款新的处理器设计而不用去做电路级的设计验证。制造一款新的处理器至少要花几个月甚至几年的时间,特别是在进入7nm工艺之后,其费用是极其昂贵的。如果这款新的处理器制造出来仅仅是为了验证设计,若有问题,必须进行修改、重新制造,并再进行验证,这种方式所花的成本和时间是任何一家公司都不能接受的。因此,利用高效的仿真建模工具对处理器体系结构的设计方案进行充分的量化分析是确保处理器性能、缩短面世周期、降低设计成本的必由之路!

总的来说,对处理器体系结构进行建模和仿真具有以下几个方面重要意义:

1、缩短处理器的设计和开发周期,节约开发成本;

2、帮助设计人员找出处理器中具有更多设计空间的部分,以便进一步研究或设计;

3、可在没有硬件实物的条件下对新的处理器体系结构进行验证;

4、有助于对处理器系统性能指标进行测量;

5、帮助学术界对处理器结构进行学术研究;

6、有利于教育机构对计算机系统结构进行形象生动的教学。

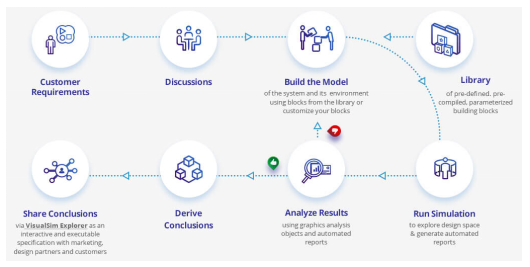

2. 仿真工具VisualSim概述

VisualSim是一个面向电子系统和半导体产品的建模、仿真和探索软件平台。它采用基于模型的系统工程(MBSE,Model-based System Engineering)和电子系统级(ESL,Electronic System Level)设计方法填补了设计规范和设计实现之间的鸿沟。对于电子系统产品,VisualSim能够提供系统设计的时序和功耗仿真;对于半导体产品,VisualSim能够提供周期级精确的早期性能和功耗分析。

通过在VisualSim中建模和仿真,架构师能够根据性能和功耗的报告识别、解决系统性能瓶颈,确保不存在过设计或者欠设计,实现电子系统整体的性能优化和权衡,确保电子产品的设计规范得到充分的测试和优化,防止在产品实现过程中发生大规模性能偏离的情况。

本文针对处理器体系结构设计需求,通过两个案例说明基于VisualSim开展处理器建模与仿真的效果。

3. 案例1:处理器微结构建模与仿真

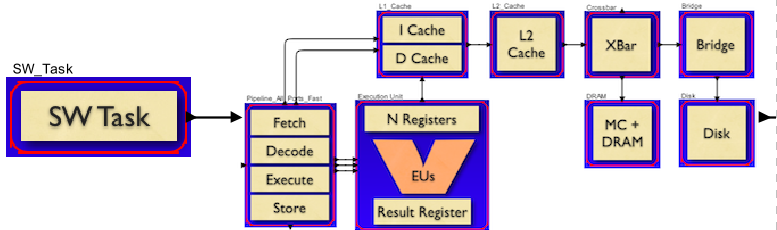

一、处理器微架构建模对象介绍

处理器微架构及其外部总线和存储设备如图所示。其中,处理器微架构由流水线、regfile、定点ALU(ALU_INT)、浮点ALU(ALU_FP)、哈佛结构的L1高速缓存和冯诺依曼结构的L2高速缓存组成。L2高速缓存外部连接Crossbar,通过Crossbar连接DRAM和桥接的磁盘,以此构成一个完整的计算系统。

二、基于VisualSim的处理器微架构建模与仿真

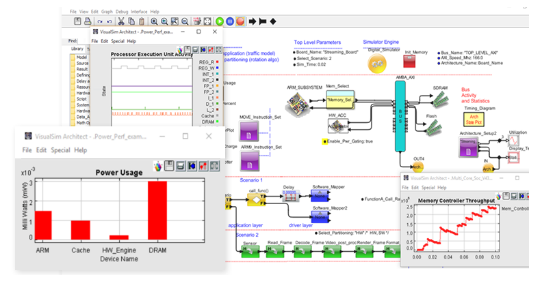

(1) 处理器微架构模型总体设计

处理器微架构模型总体设计如图所示,包括4级流水线、处理器内部regfile及定/浮运算单元、高速缓存、外部总线及存储器四个主要部分。同时,为了分析处理器微架构的运行工况和功耗,还增加了软件模块和功耗模块。后续章节将对这些模块进行详细说明。

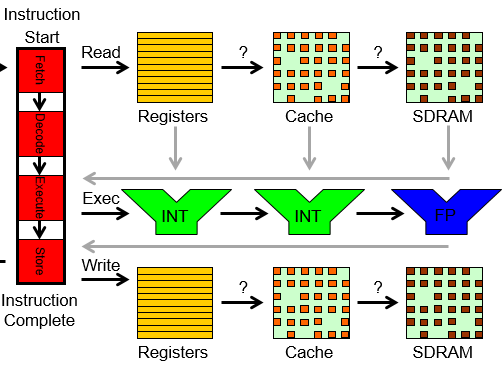

(2) 流水线

流水线结构及其与cache、regfile、片外存储器的关系如图3-3所示。其中,流水线包括4级,分别是Fetch、Decode、Execute和Store,运算单元包括两个整数运算单元和一个浮点运算单元。流水线模型强调对处理器内、外部资源的使用,而不是建模各级流水线的详细功能,这是处理器架构建模的一个常用方法。

流水线的基本工作过程如下:

Fetch:流水线收到指令,根据组中的每一条指令,对存储器接口产生读操作,同时判断指令是定点指令还是浮点指令,之后触发Decode级;

Decode:向cache发出读数命令,之后触发Execute级;

Execute:根据当前执行的指令,触发并等待定点或者浮点执行单元完成,之后触发Store级;当流水线执行完成当前程序中的所有指令后,计算处理器微架构MIPS等参数,并触发下一段程序指令进入流水线;

Store:将指令执行的结果写回到cache中。

(3) regfile与运算单元

regfile与运算单元在处理器微架构模型中重点建模运行时的延时,其值根据执行指令的不同而不同,因此,在VisualSim中对处理器微架构中支持的每一条指令的延迟进行标注,执行不同指令时,regfile与运算单元会产生不同的延时,该延时会标注到模型中各模块间传递数据的数据结构(DS)中,以便仿真过程其他模块使用。

(4) 高速缓存

处理器微架构模型中的高速缓存分为L1和L2两级,其中L1为哈佛结构,指令cache和数据cache相互独立,L2为冯诺依曼结构,指令与数据混合cache。当指令或者数据的读写请求发送到cache后,cache根据命中率等参数决定cache行为,当cache不命中时,向下一级cache或者总线发出操作请求。

(5) 外部总线及存储器

在处理器微架构模型中,外部总线及存储器的作用主要是为了配合流水线的运行,在效果上类似于IC设计中Testbench内部模拟与DUT连接的其他部件功能。处理器微架构模型中的外部总线及存储器包括与L2 cache连接的Crossbar、与Crossbar连接的DRAM(含存储器控制器)、与Crossbar连接的桥、通过桥与Crossbar连接的磁盘,共4部分。这四个模块主要用来模拟流水线对外部存储设备进行读写操作时的动作和延迟,四个模块都会产生自身的工况。

(6) 程序

程序对于处理器微架构来说是一种激励。在本模型中,程序以进程或者线程为最小单位,即:程序模块以一定的延迟循环向流水线发送一个指令组,每个指令组中包含一个进程或者一个线程内部全部的指令。在指令组发送到流水线模型之前,会暂存在一个buffer当中,当流水线执行完成前一个指令组中的所有指令后,则告知buffer“弹出”下一个指令组。在指令组从buffer弹出、进入流水线之前的这段时间中,还进行了一段延时,用于模拟流水线切换进程或线程时产生的时延。

(7) 仿真结果

a.仿真结果收集

Ø 处理器微架构各部件的工况收集

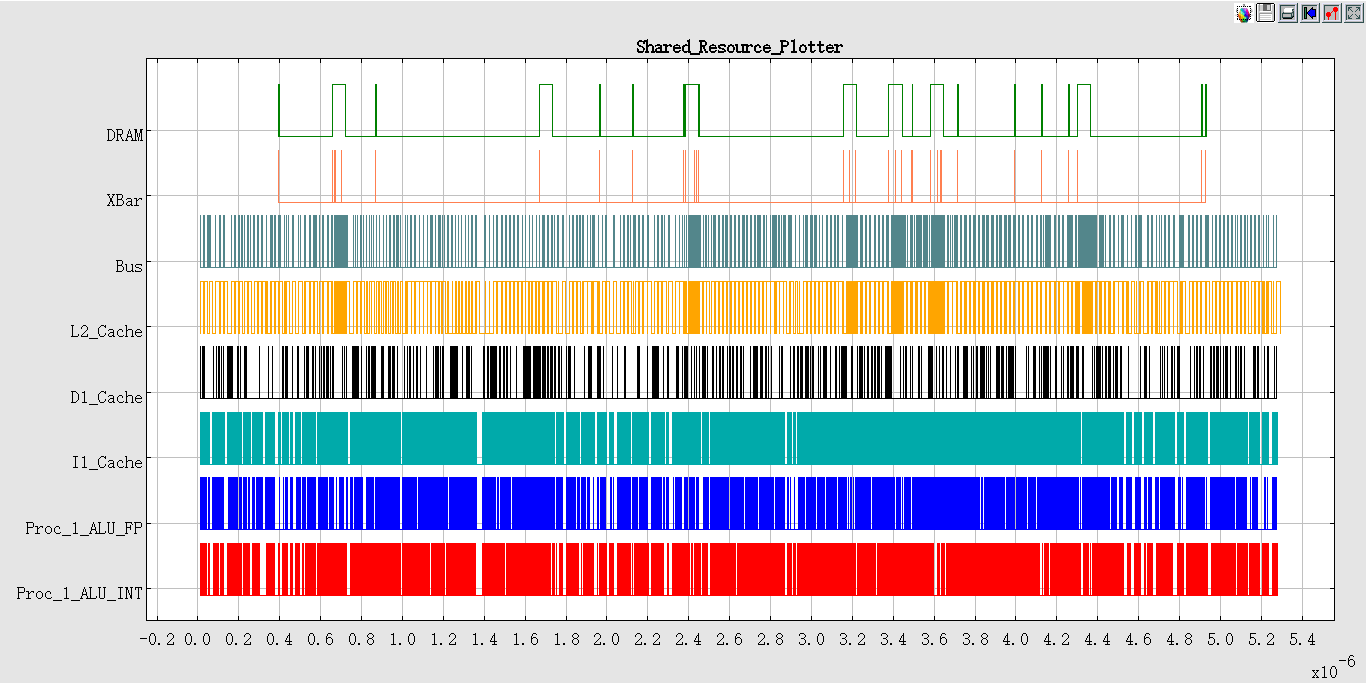

在处理器微架构模型中专门设置了一个收集各部件工况的模块,称为“Shared_Resouces”。该模块收集处理器微架构中整数单元、浮点单元、一级指令cache、一级数据cache、二级cache、一/二级cache间总线、处理器外部Crossbar、DRAM,共8个部件的工况。当上述8个部件活动时,会将活动信息输送到工况收集模块,工况收集模块根据收到各部件工况的时间点和设定的各部件工作时间,把工况显示为图形。

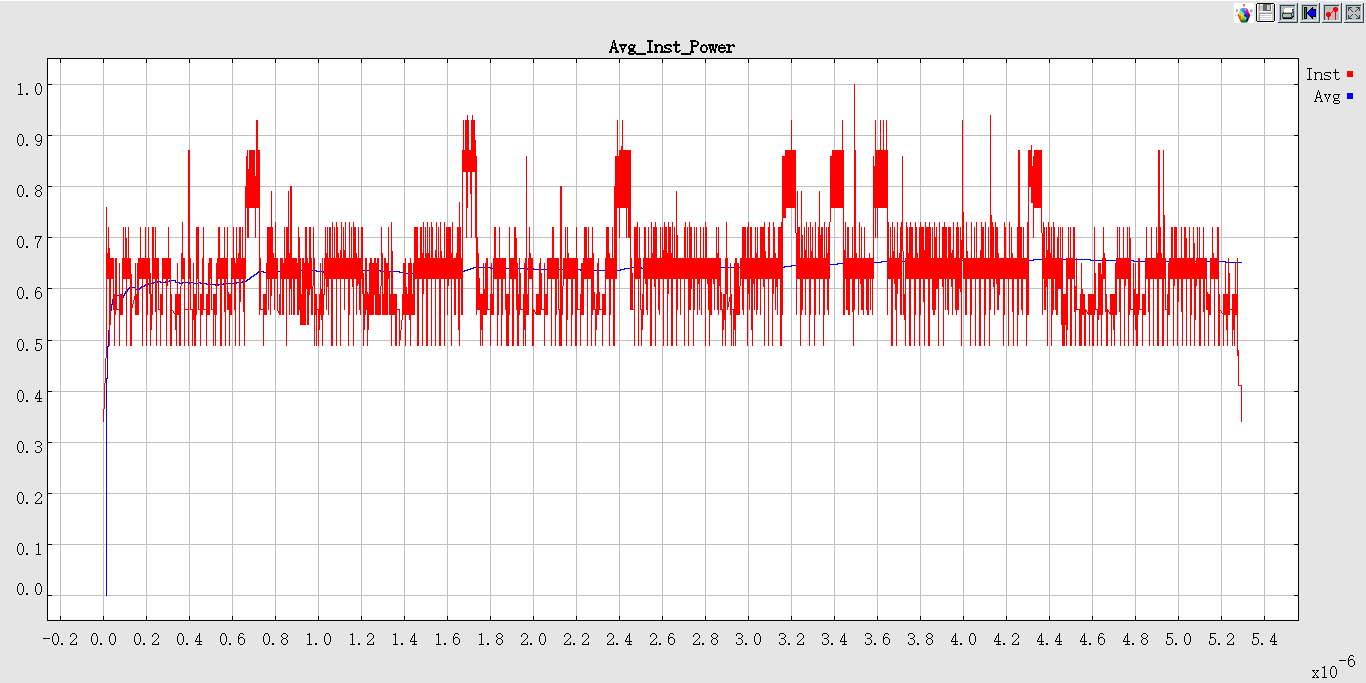

Ø 处理器微架构各部件的功耗收集

在处理器微架构模型中,设置了一个功耗计算模块,该模块设置了处理器微架构模型中各部件待机(Standby)和活动(Active)时的功耗值。与此同时,处理器微架构模型的各个部件在执行中会设置当前工作状态为待机或者活动,并把这个工作状态发送给功耗计算模块。当功耗计算模块接收到处理器微架构中各模块的工作状态后,会根据工作状态查找相应的功耗值并计算模型瞬时和平均功耗,并将两个功耗值以折线图方式显示。

b.仿真结果显示

处理器微架构模型的仿真结果主要包括微架构工况、微架构中流水线功耗以及微架构主要性能参数,具体如下:

Ø 处理器微架构工况

处理器微架构工况如图所示。该图中分别用红、蓝等8种不同颜色的线条表征了处理器微架构中整数单元、浮点单元、一级指令cache、一级数据cache、二级cache、一/二级cache间总线、处理器外部Crossbar、DRAM,共8个模块的工作情况及其相互之间的时序关系。对于某一个部件来说,当其线条为高时,表示其在工作,为低时,表示其不在工作;高或者低线条维持的时间,表示这种状态持续的时间。通过处理器微架构工况图,可以清晰的观测到在当前微架构设计中各个模块间的协作关系,能够分析微架构设计是否与预期一致、是否存在设计瓶颈等诸多问题。

Ø 处理器微架构中流水线功耗

对于流水线功耗,当流水线进入Fetch级,即流水线开始工作时,将流水线工作状态设置为Active;当流水线执行完Execute级、进入Store级时,流水线的工作完成,此时将流水线的工作状态设置为Standby。功耗计算模块收集到流水线工作状态的变化,通过查找内部工作状态与功耗值的对应表,计算得到流水线实时与平均功耗值,如图所示。通过流水线功耗图,可以清晰的观测到流水线在工作中产生的功耗情况,特别是功耗峰值和功耗低谷。通过功耗峰值和功耗低谷发生的时间和长度,分析流水线中相应部件的具体工作状况,可以找到产生功耗峰值和功耗低谷的具体原因,以便继续优化流水线性能。

Ø 处理器微架构主要性能参数

处理器微架构主要性能参数包括CYCLES_IN_PROCESSOR、CYCLES_PER_INSTRUCTION、MIPS_IN_PROCESSOR、TIME_IN_PROCESSOR,这些参数总体上表征了当前处理器微架构设计在运行当前程序激励时的性能指标,如图所示。结合微处理器架构工况、流水线功耗的报告,可以从宏观和微观两种角度对当前处理器微架构进行观察,提取特征、发现问题,为优化提高处理器微架构设计、提高性能提供有效支撑。

4. 案例2:处理器外部存储器功耗与温度建模与仿真

一、处理器外部存储器系统建模对象

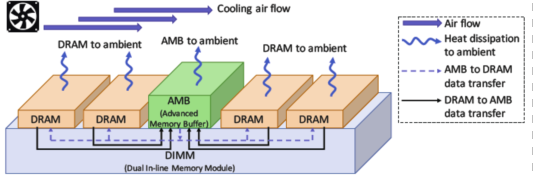

处理器外部存储器与处理器的性能息息相关,良好的功耗与温度设计对于处理器应用系统,特别是嵌入式应用具有非常重要的意义。本案例所述建模对象为双列直插内存模块(Dual In-line Memory Module,DIMM),如图所示。其中,DIMM由高级存储器缓存(Advanced Memory Buffer,AMB)和DRAM颗粒两部分组成,AMB实现处理器与DRAM颗粒之间的数据连接和缓存。在DIMM上方有一个散热风扇,风扇出风横向流过DIMM表面,对AMB和DRAM颗粒进行散热。

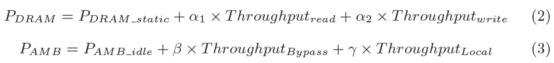

DIMM功耗由静态功耗和动态功耗两部分组成,例如DRAM颗粒的功耗由式(1)计算得到。

由于动态功耗由AMB和DRAM颗粒内部流过的数据量决定,因此DIMM的功耗计算如式(2)、(3)所示。其中,PDRAM_static和PAMB_idle分别表示DRAM颗粒和AMB的静态功耗,Throughputread、Throughputwrite、ThroughputBypass、ThroughputLocal表示DRAM颗粒和AMB在不同状态时的数据吞吐量,α1、α2、β、γ为吞吐量的系数,具体数值可参考Lin, Jiang, et al的文章。

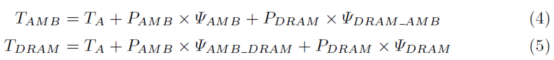

在DIMM功耗计算的基础上,可以对温度进行计算,如式(4)、(5)。其中,TA表示DIMM在不工作时的稳定温度,ψAMB、ψDRAM_AMB、ψAMB_DRAM、ψDRAM分别表示DIMM上各部件的热阻。利用式(4)、(5)可以计算出DIMM工作时的实时温度。

二、基于VisualSim的处理器外部存储器功耗与温度仿真

(1) 处理器外部存储器功耗与温度仿真模型总体设计

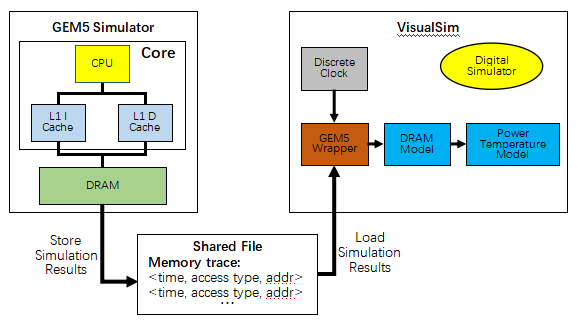

由上述功耗和温度计算公式可知,两者仿真精确度依赖于处理器对存储器的访问模式和数据吞吐量,为了能够尽可能获得高精度的仿真结果,本案例采用GEM5和VisualSim联合仿真的方式实现。

其中,在GEM5侧,模拟一个包含CPU、哈佛结构的L1高速缓存和DRAM的小型处理器,该处理器运行真实的程序。程序运行过程中,产生对DRAM的操作,可称其为存储器访问跟踪结果。该结果包含时间、访问类型、地址等数据,存储在计算机磁盘的共享文件中。在VisualSim侧,利用其自带的GEM5 Wrapper模块读取计算机磁盘中的共享文件,获得其中GEM5运行真实程序时对DRAM的操作跟踪结果。GEM5 Wrapper从跟踪结果中读取相应的数据,完成GEM5和VisualSim两侧的时钟同步,计算DRAM吞吐量,进而计算得到DRAM的功耗和温度,并以图形化的方式显示出来。

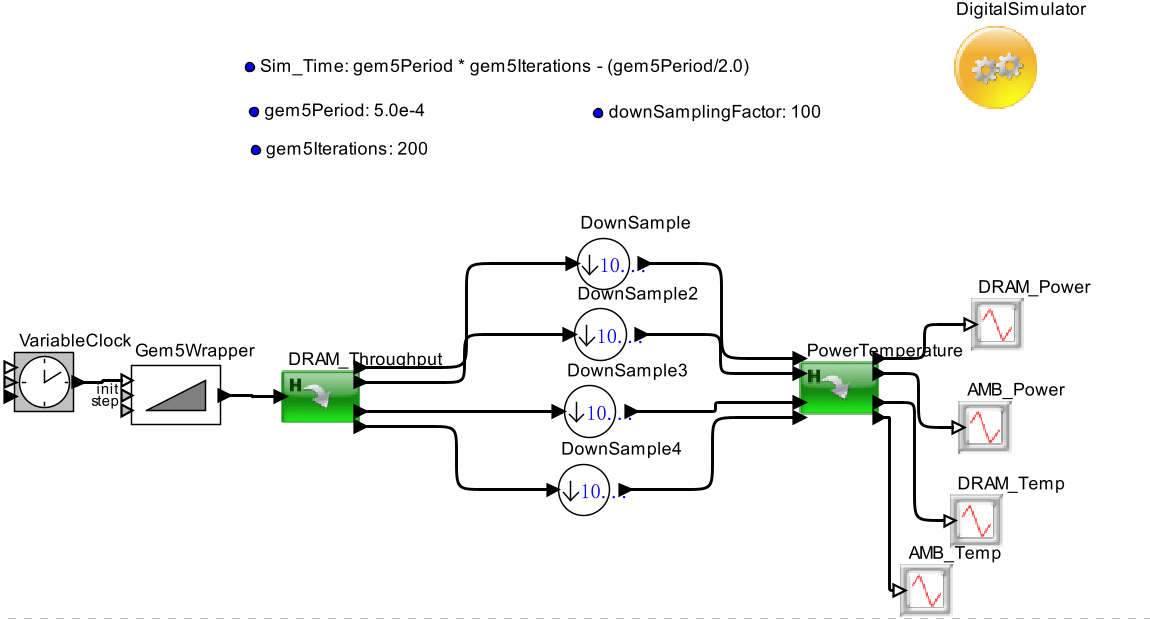

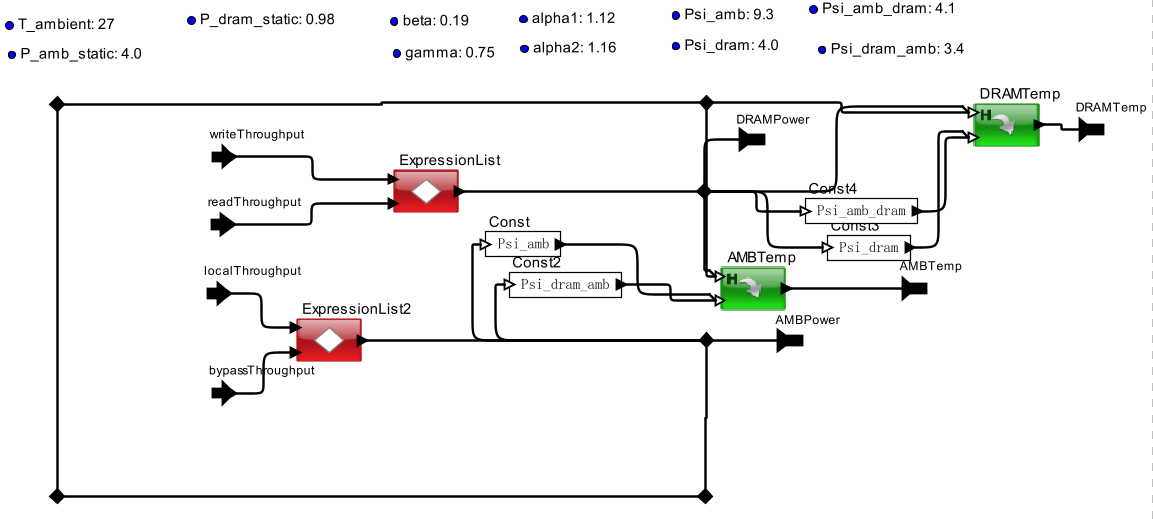

根据此方案,基于VisualSim建立的模型如图所示。

(2) GEM5

GEM5是一款模块化的离散事件驱动全系统模拟器,它结合了M5和GEMS中最优秀的部分,M5提供了高度可配置的模拟框架,支持多种ISAs和CPU模型;GEMS补充了M5的特性,提供了详细而灵活的内存系统,包括多种cache一致性协议和互连模型,是一款高度可配置、集成多种ISA,多种CPU模型的体系结构模拟器。

GEM5模拟器目前支持多种ISAs,包括Alpha、ARM、MIPS、Power、SPARC和x86。模拟器的模块性允许这些不同的ISAs插入到通用CPU模型和内存系统中,而不需要为每一种ISAs设置一种专用的CPU模型和存储模型,这使得模拟器模块化程度较高且易于在不同CPU之间切换。

在本案例中,GEM5模拟运行在1GHz、使用DDR3的ARM处理器执行Mibench程序,在此过程中产生的对DRAM的操作作为激励输入到VisualSim中以便仿真功耗和温度。

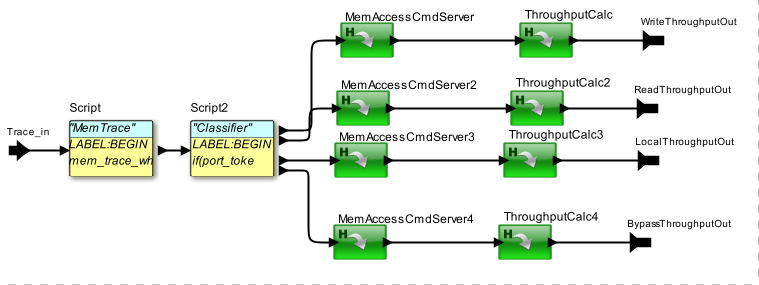

(3) DRAM吞吐量计算

计算DRAM吞吐量之前,首先根据DRAM的read、write、bypass、非bypass四种操作模式对存储器操作跟踪进行分类,之后使用存储器位宽乘以存储器操作的数据量,再除以这一段存储器跟踪的时长,得到这一段DRAM操作的吞吐量。如图所示。

(4) 功耗与温度建模

功耗与温度建模的方式,如图所示。

(5) 仿真结果

对处理器外部存储器系统功耗和温度的仿真激励采用Mibench。MiBench是密歇根大学(The University of Michigan)电子工程与计算科学学院推出的一个免费的嵌入式基准测试集合,其共包含35个嵌入式程序,分成汽车及工业制造、消费电子、办公自动化、网络、安全、通信六个子类。所有程序都使用ANSI C编写,这使得MiBench具有很好的可移植性。本案例以Mibench中的JPEG编解码程序为代表,演示通过GEM5和VisualSim的联合仿真实现对处理器外部存储器系统功耗和温度的仿真结果。

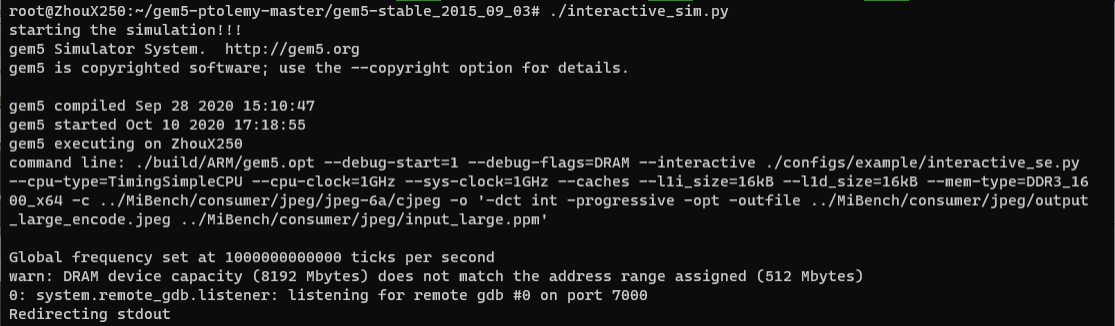

仿真时首先启动GEM5,如图所示。GEM5启动后,会等待VisualSim的连接。

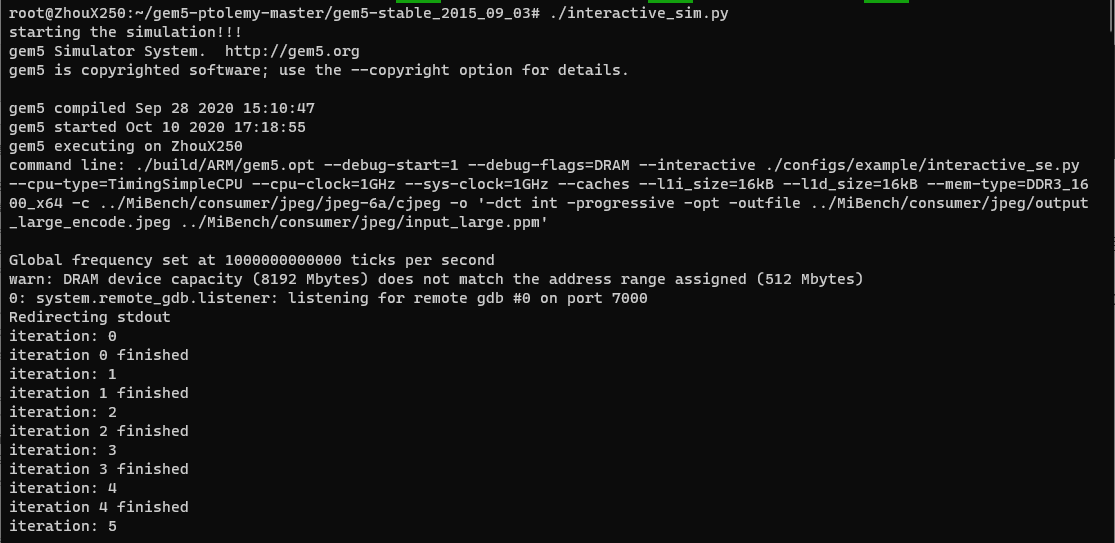

此时启动VisualSim仿真,在GEM5会看到双方相互传输存储器访问跟踪结果,如图所示。与此同时,VisualSim也开始根据存储器访问跟踪结果计算处理器外部存储器系统的功耗和温度变化。

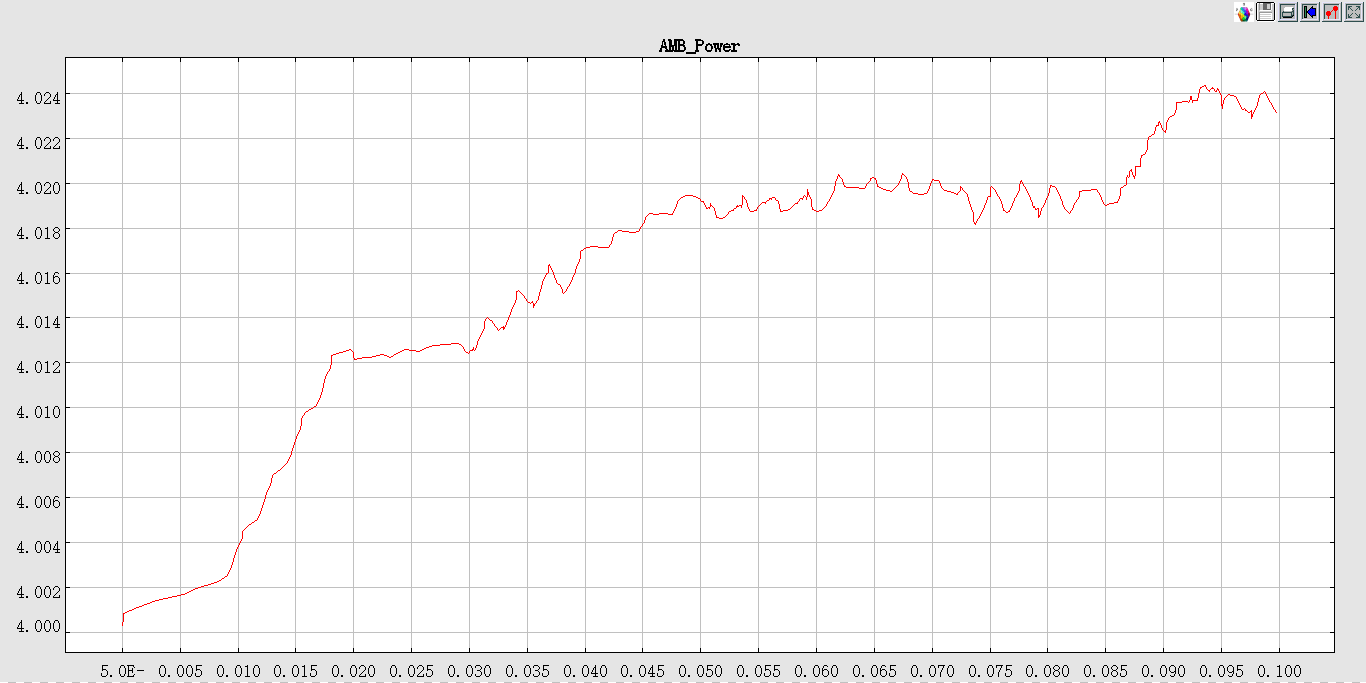

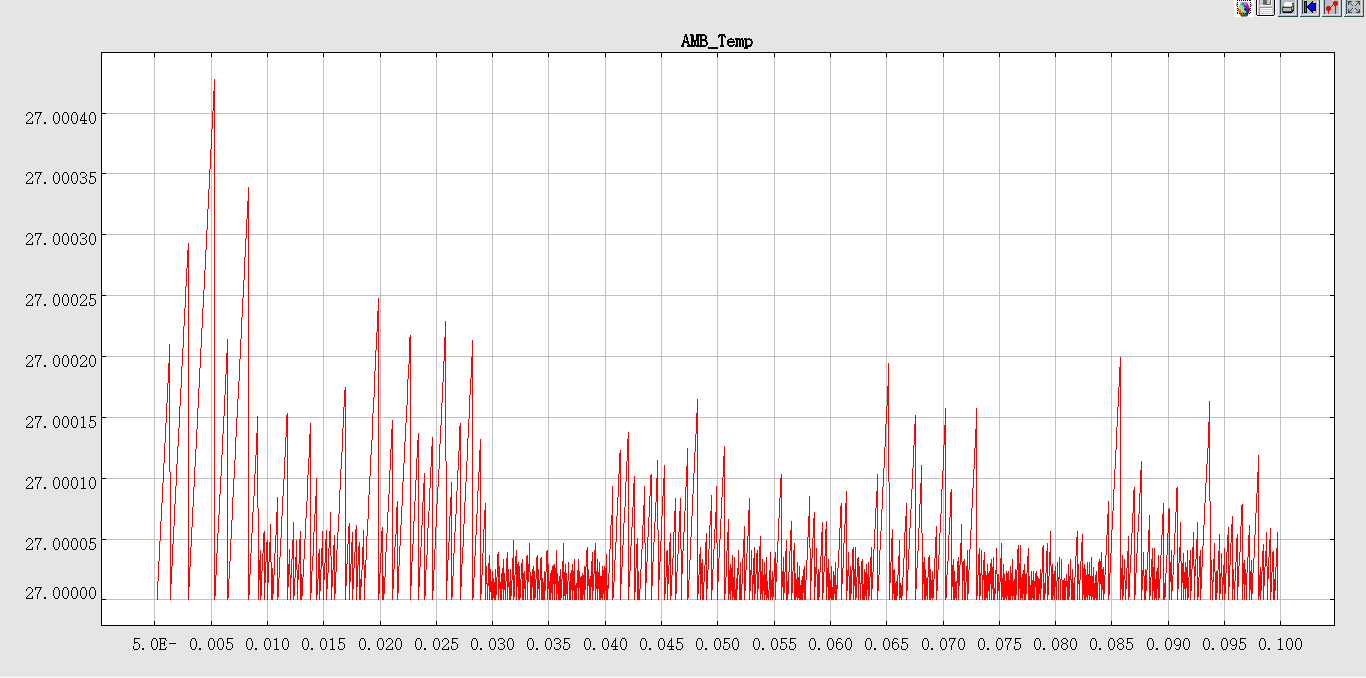

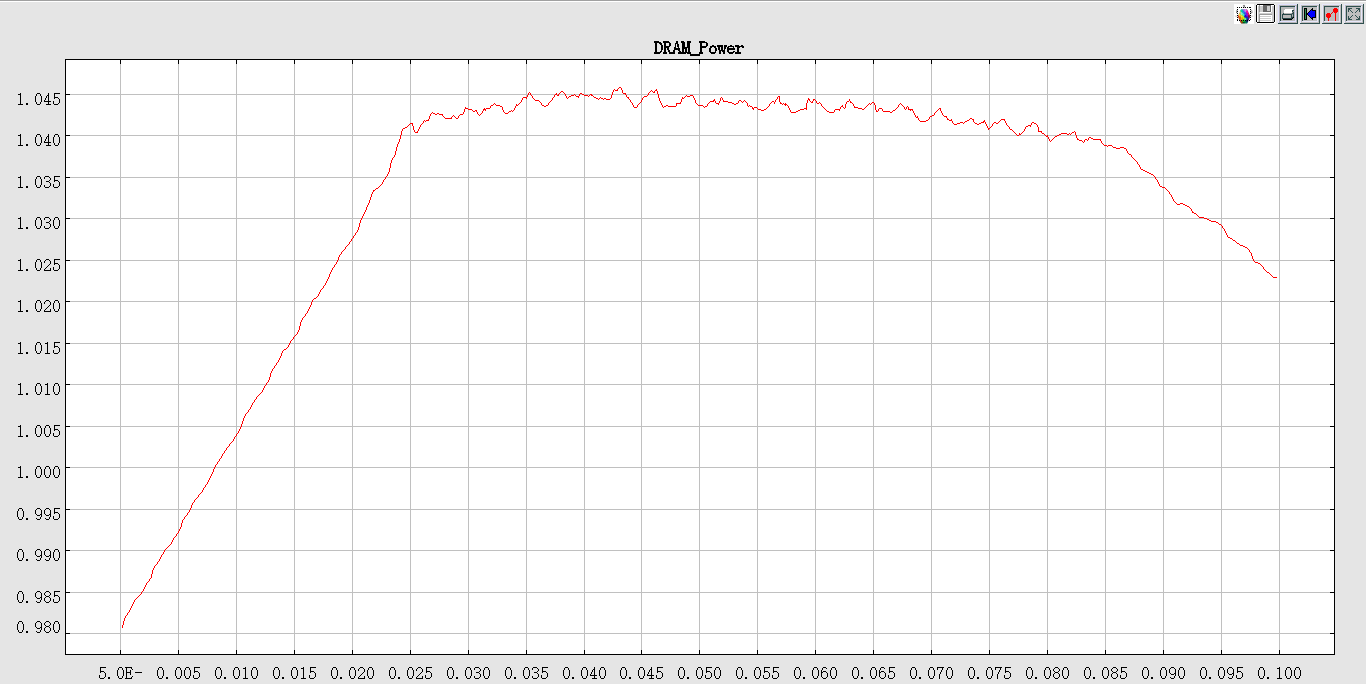

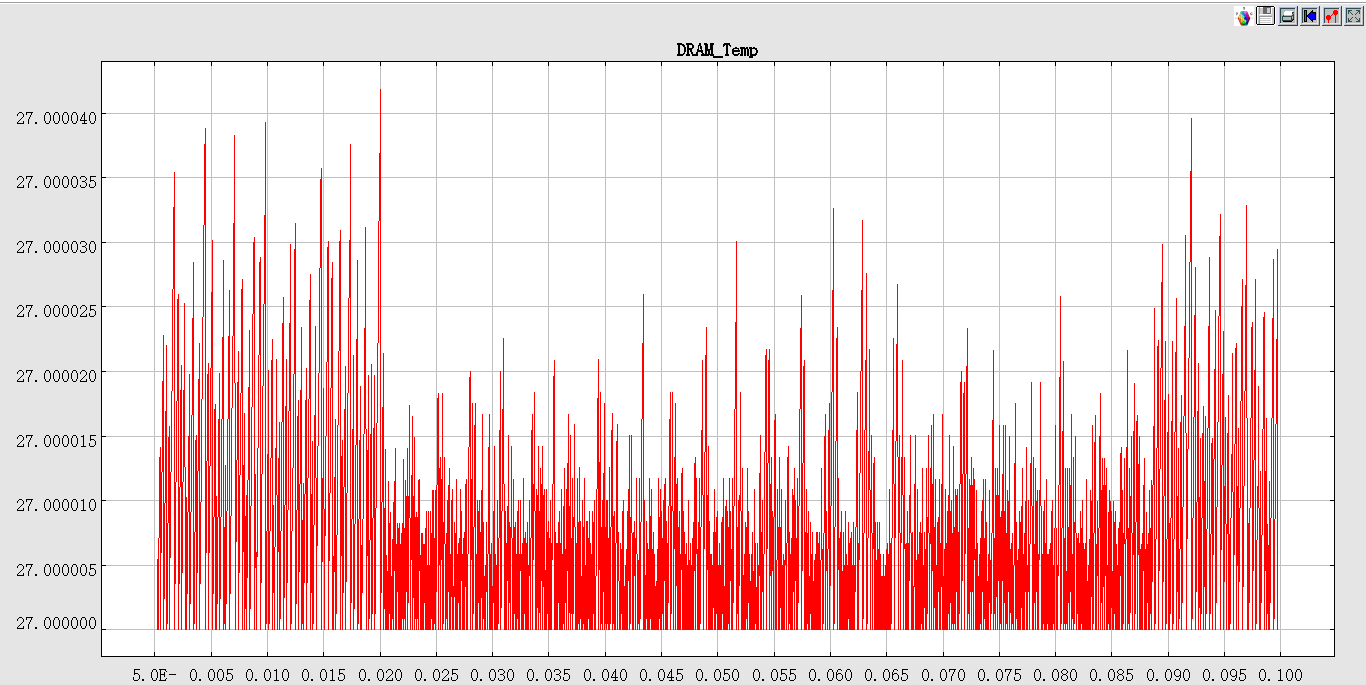

运行Mibench的JPEG编解码程序时,处理器外部存储器系统中AMB和DRAM颗粒的功耗和温度分别如图所示。根据仿真结果可知,对于AMB和DRAM颗粒,在运行JPEG编解码程序过程中,无论是功耗还是温度都有所提升,但总体增幅不大;对于AMB其温度呈现了数个小型尖峰,而对于DRAM颗粒其温度总体上呈现仿真开始后、结束前较高,中间较低的情况。通过GEM5和VisualSim的联合仿真,可以清晰将处理器外部存储器系统的功耗和温度变化呈现出来,供工程师进行观察和分析,进而优化处理器及其应用系统的设计。